| Select | Platform | Category | Node / Tech | Org | License | Maturity | First Release | Last Update | Links |

|---|

| Platform | Node / Tech | Org | License | Maturity | Foundry |

|---|

| Platform | Tech | Org | License | Maturity | Notes |

|---|

| Platform | Type | Org | License | Maturity | Notes |

|---|

| Core | ISA / Profile | Family | License | Maturity | Typical Use |

|---|

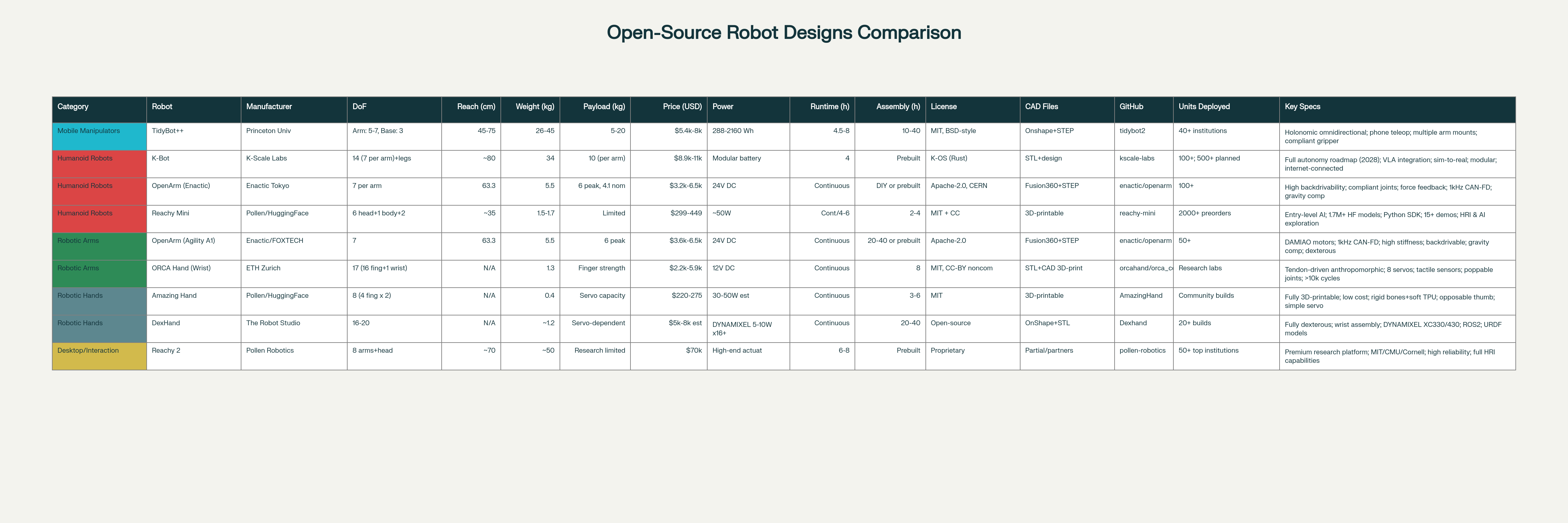

Comprehensive Specifications Overview

High-level comparison of process nodes, open-source status, and integration stacks across PDKs, SoCs, and cores.

License Information

Apache 2.0

Commercial Use: Yes

Restrictions: Attribution and patent grant conditions

Applies To: SKY130, GF180MCU, many PULP artifacts

MIT / ISC / BSD

Commercial Use: Yes

Restrictions: Minimal; include copyright and license

Applies To: VexRiscv, PicoRV32, many RISC-V cores

Custom Open PDK

Commercial Use: Yes (with conditions)

Restrictions: Share-alike and documentation-specific terms

Applies To: IHP SG13G2 Open Source PDK

Commercial / NDA PDK

Commercial Use: Yes (under NDA and foundry contracts)

Restrictions: Redistribution limits, MPW programme rules

Applies To: AIM Photonics PDKs, many Arm-based SoCs

Cost & Access Tiers

-

Fully Open & Free

Best for: Early research, teaching, community MPW.

Platforms: SKY130, GF180MCU, IHP SG13G2, Open_PDKs, PicoRV32, VexRiscv, Chipyard and PULP SoCs.

-

Low-Cost Research (Fees / MPW)

Best for: University chips, startup prototypes, shared shuttles.

Platforms: Open PDKs with MPW runs; PULP / Chipyard taped out on SKY130 or GF180.

-

Commercial PDK & IP

Best for: Product SoCs, photonic modules, high-volume integration.

Platforms: AIM Photonics PDKs, proprietary CMOS nodes, Arm and licensed RISC‑V cores.

Critical Decision Factors

-

Process & Node

How does feature size and device mix match your constraints?

- 130/180 nm open nodes work well for digital control and mixed-signal.

- BiCMOS and RF options matter for analog-heavy designs.

- Photonic PDKs add waveguides, couplers, and detectors.

-

Tooling & Integration

Can your team run the full flow with open or licensed EDA?

- Open_PDKs and IIC‑OSIC‑TOOLS enable full open flows on SKY130 and GF180.

- SoC generators (Chipyard, PULP) accelerate RISC‑V integration.

- Photonic design often requires specialised layout and simulation tools.

-

IP & Licensing

What are your obligations around redistribution and derivatives?

- Apache, MIT, ISC, BSD are permissive with attribution.

- Custom open PDKs may enforce share-alike requirements.

- Commercial PDKs and Arm IP require NDAs and paid licences.

-

Timeline & Risk

How quickly must you tape out and iterate?

- Open MPWs favour frequent, low-cost iterations.

- Commercial runs need more up-front validation and NRE.

- Reuse of proven cores reduces bring-up risk.

Deployment Scale Guidance

-

Academic Labs & Makers (1–5 chips)

Recommended: SKY130 / GF180 PDKs, Open_PDKs, IIC‑OSIC‑TOOLS, PicoRV32 or VexRiscv cores, Chipyard demo SoCs.

Priority: Documentation, community examples, simple flows, low tapeout cost.

-

Startups & Research Prototypes (5–50 chips)

Recommended: SKY130 / GF180 with PULP or Chipyard SoCs; mixed-signal extensions on IHP SG13G2.

Priority: Integration with standard toolchains, reproducible flows, clear IP position.

-

Commercial Products (50+ chips)

Recommended: Commercial CMOS and photonic PDKs, licensed Arm or high-end RISC‑V, professional EDA.

Priority: Yield, foundry support, long-term IP agreements, safety certification.